晶体管是芯片组成的基本单位,如果说芯片是房子,那么晶体管就是组成房子的砖块。随着工艺与制程的提升,单个芯片上能够容纳的晶体管数量越来越多。指甲盖那么大小的芯片现在已经可以容纳几十亿个晶体管。

在上一讲中我们知道,通过对栅极电压的控制可以控制晶体管的通断状态,从而实现逻辑的控制。

在实际设计使用中,对栅极电压的控制是工艺以及生产厂追求的指标。如何用尽量小的电压控制电路的状态体现了foundry厂的工艺能力。

我们常说的7nm,3nm等,是指的晶体管内部控制电子流动的栅极长度。一个晶体管是由源极(source)、漏极(Drain)、栅极(Gate)组成,电流从源极经栅极流向漏极,就代表晶体管导通,栅极就是控制导通与否的开关。

而先进的制程就是将这个开关做的尽量的窄,当栅极做窄之后,所需要的控制电压对应也会降低,从而整体降低了晶体管开关的功耗以及发热问题。

栅极变小对应整个晶体管的面积就会变小,我们就可以在相同面积下放更多的晶体管。这也是实现摩尔定律快速发展一贯遵循的思路。因为一颗原子的大小大概是0.1nm,所以制程约先进留给原子的空间越小,也会造成约不稳定。一味地通过缩小栅极长度是无法突破原子大小极限的,于是人们就开始采用其他的思路来解决目前遇到的问题。

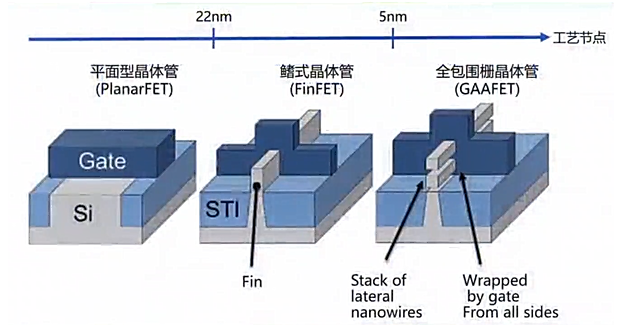

随着制程的发展,晶体管也出现了不同的技术模式,从平面型切换到鳍式晶体管(FinFET),到目前最先进的全包围栅(GAAFET)。更高级的制程需要更好的技术与创新才能实现,目前技术研发正在探索更加有效的方式。同样新材料的研发也是促进技术进步的源泉。目前市面已有多种材料研取得突破进展,石墨烯也是一种发展方向,但是从研究到应用需要一个成本与效率的转化过程。